Number 852

# Bluespec Extensible RISC Implementation: BERI Hardware reference

Robert N.M. Watson, Jonathan Woodruff, David Chisnall, Brooks Davis, Wojciech Koszek, A. Theodore Markettos, Simon W. Moore, Steven J. Murdoch, Peter G. Neumann, Robert Norton, Michael Roe

April 2014

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500 http://www.cl.cam.ac.uk/

© 2014 Robert N.M. Watson, Jonathan Woodruff, David Chisnall, Brooks Davis, Wojciech Koszek, A. Theodore Markettos, Simon W. Moore, Steven J. Murdoch, Peter G. Neumann, Robert Norton, Michael Roe

SRI International is acknowledged as an additional copyright holder

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

### **Abstract**

The *BERI Hardware Reference* describes the Bluespec Extensible RISC Implementation (BERI) protoype developed by SRI International and the University of Cambridge. The reference is targeted at hardware and software developers working with the BERI1 and BERI2 processor prototypes in simulation and synthesized to FPGA targets. We describe how to use the BERI1 and BERI2 processors in simulation, the BERI1 debug unit, the BERI unit-test suite, how to use BERI with Altera FPGAs and Terasic DE4 boards, the 64-bit MIPS and CHERI ISAs implemented by the prototypes, the BERI1 and BERI2 processor implementations themselves, and the BERI Programmable Interrupt Controller (PIC).

## Acknowledgments

The authors of this report thank other members of the CTSRD team, and our past and current research collaborators at SRI and Cambridge:

| Ross J. Anderson  | Jonathan Anderson | Gregory Chadwick  | Nirav Dave          |

|-------------------|-------------------|-------------------|---------------------|

| Khilan Gudka      | Jong Hun Han      | Alex Horsman      | Alexandre Joannou   |

| Asif Khan         | Myron King        | Ben Laurie        | Patrick Lincoln     |

| Anil Madhavapeddy | Ilias Marinos     | Ed Maste          | Andrew Moore        |

| Will Morland      | Alan Mujumdar     | Prashanth Mundkur | Philip Paeps        |

| Colin Rothwell    | John Rushby       | Hassen Saidi      | Hans Petter Selasky |

| Muhammad Shahbaz  | Stacey Son        | Richard Uhler     | Philip Withnall     |

| Bjoern Zeeb       |                   |                   |                     |

The CTSRD team wishes to thank its external oversight group for significant support and contributions:

| Lee Badger      | Simon Cooper        | Rance DeLong | Jeremy Epstein |

|-----------------|---------------------|--------------|----------------|

| Virgil Gligor   | Li Gong             | Mike Gordon  | Steven Hand    |

| Andrew Herbert  | Warren A. Hunt Jr.  | Doug Maughan | Greg Morrisett |

| Brian Randell   | Kenneth F. Shotting | Joe Stoy     | Tom Van Vleck  |

| Samual M. Wahar |                     |              |                |

Samuel M. Weber

Finally, we are grateful to Howie Shrobe, MIT professor and past DARPA CRASH program manager, who has offered both technical insight and support throughout this work. We are also grateful to Robert Laddaga, who has succeeded Howie in overseeing the CRASH program.

# **Contents**

| 1 | Intr | oduction                                          | 8  |

|---|------|---------------------------------------------------|----|

|   | 1.1  | Bluespec Extensible RISC Implementation (BERI)    | 8  |

|   | 1.2  | BERI and BERI2 Prototypes                         | 8  |

|   | 1.3  | The CHERI Capability Model                        | 9  |

|   | 1.4  | Getting BERI                                      | 9  |

|   | 1.5  | Using BERI                                        | 9  |

|   | 1.6  | Licensing                                         | 9  |

|   | 1.7  |                                                   | 10 |

|   | 1.8  | Document Structure                                | 11 |

| 2 | Sim  | ulating BERI                                      | 12 |

|   | 2.1  | Software Dependencies to Build BERI               | 12 |

|   |      | 2.1.1 Installing Bluespec System Verilog compiler | 12 |

|   |      | 2.1.2 Ubuntu Package Dependencies                 | 12 |

|   |      | 2.1.3 Installing the GCC Compiler                 | 13 |

|   |      | 2.1.4 Installing the CHERI MIPS assembler         | 13 |

|   |      |                                                   | 13 |

|   | 2.2  | Extracting a BERI Release                         | 14 |

|   | 2.3  | Checking Out the Development Version of BERI      | 14 |

|   | 2.4  | Configuring the Build Environment                 | 15 |

|   | 2.5  | Building the BERI Simulator                       | 15 |

|   | 2.6  | Configuring the BERI Simulator                    | 16 |

|   | 2.7  | Simulating BERI                                   | 16 |

|   | 2.8  | Running the BERI Test Suite                       | 16 |

| 3 | Usir | ng the BERI1 Debug Unit                           | 18 |

|   | 3.1  | Communicating with the BERI Debug Unit            | 18 |

|   | 3.2  | BERI Debug Registers                              | 18 |

|   | 3.3  | BERI Debug Instructions                           | 19 |

|   | 3.4  | BERI Debug Responses                              | 20 |

| 4 | The  | BERI Unit Test Suite                              | 22 |

|   | 4.1  | The BERI Unit Test Environment                    | 22 |

|   | 4.2  | Software Dependencies                             | 22 |

|   |      | 4.2.1 BERI Test-Suite Directory Layout            | 23 |

|   |      |                                                   | 23 |

|   |     | 4.2.3 Unit Test Support Library                          |

|---|-----|----------------------------------------------------------|

|   | 4.3 | Running the BERI Test Suite                              |

|   |     | 4.3.1 Jenkins                                            |

|   | 4.4 | Unit Test Structure                                      |

|   |     | 4.4.1 Test Types                                         |

|   |     | 4.4.2 Test Structure                                     |

|   |     | 4.4.3 Test Termination                                   |

|   |     | 4.4.4 Connecting New Tests to the Build                  |

|   |     | 4.4.5 Test Attributes                                    |

|   | 4.5 | Unit Test Support Library                                |

|   |     | 4.5.1 Multithreading                                     |

|   | 4.6 | Example Unit Test: Register Zero                         |

|   |     | 4.6.1 Register Zero Test Code                            |

|   |     | 4.6.2 Register Zero Nose Assertions                      |

|   | 4.7 | Conclusion                                               |

|   | ,   | Conclusion                                               |

| 5 | BER | I on Altera FPGAs 33                                     |

|   | 5.1 | Building BERI for Synthesis                              |

|   | 5.2 | The Altera Development Environment                       |

|   | 5.3 | Synthesizing BERI                                        |

|   |     |                                                          |

| 6 | BER | I on Terasic Boards 3'                                   |

|   | 6.1 | BERI Configuration on Terasic FPGA Boards                |

|   |     | 6.1.1 Physical Address Space on the DE4                  |

|   |     | 6.1.2 Physical Address Space on the tPad                 |

|   | 6.2 | Altera IP Cores                                          |

|   | 6.3 | Cambridge IP Cores                                       |

|   |     | 6.3.1 The DE4 Multitouch LCD                             |

|   |     | 6.3.2 HDMI Chip Configuration via I2C                    |

|   | 6.4 | Standalone HDMI Output                                   |

|   |     | 6.4.1 Reconfigurable Video Pixel Clock                   |

|   |     | 6.4.2 HDMI Timing Driver                                 |

|   | 6.5 | Temperature and fan control                              |

|   | 6.6 | Terasic Hard Peripherals                                 |

|   |     | 6.6.1 Intel StrataFlash 64M NOR flash                    |

| _ |     |                                                          |

| 7 |     | BERI ISA 49                                              |

|   | 7.1 | BERI CPU Features and ISA                                |

|   |     | 7.1.1 MIPS Instructions                                  |

|   |     | 7.1.2 Coprocessor 0 Support                              |

|   |     | 7.1.3 Modifications to the MIPS TLB Model                |

|   |     | 7.1.4 Memory Caches                                      |

|   |     | 7.1.5 Limitations to Generic Coprocessor Support         |

|   |     | 7.1.6 Reset Exception                                    |

|   |     | 7.1.7 The BERI Floating-Point Unit (FPU)                 |

|   |     | 7.1.8 Selected Additions from Later MIPS ISA Versions 60 |

|   |     | 7.1.9 Virtual Address Space                              |

|    | 7.2 | CHERI ISA Extensions                                          | 5 |

|----|-----|---------------------------------------------------------------|---|

|    | 7.3 | BERI Implementation-defined Registers 65                      | 5 |

|    |     | 7.3.1 EInstr (CP0 Register 8, Select 1)                       | 5 |

|    |     | 7.3.2 Configuration Register 6 (CP0 Register 16, Select 6) 65 |   |

|    |     | 7.3.3 Processor Identification (CP0 Register 15, Select 0) 6  | 7 |

|    |     | 7.3.4 Core Identification (CP0 Register 15, Select 6) 6       | 7 |

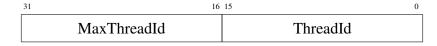

|    |     | 7.3.5 Thread Identification (CP0 Register 15, Select 7) 6     | 7 |

|    |     | 7.3.6 Stop Simulation (CP0 Register 23)                       | 7 |

|    |     | 7.3.7 Debug (CP0 Register 26, Select 0) 6                     | 7 |

|    |     | 7.3.8 Debug ICache (CP0 Register 26, Select 1) 6              | 7 |

|    | 7.4 | BERI2 Specific Features                                       | 8 |

|    |     | 7.4.1 Multi-Threading                                         | 8 |

| 8  | The | BERI1 Processor Implementation 69                             | 9 |

|    | 8.1 | Bluespec                                                      | 9 |

|    | 8.2 | Directory Layout                                              | 9 |

|    | 8.3 | Key Files                                                     | 9 |

|    | 8.4 | Conditionally Compiled Features                               | 1 |

| 9  | The | BERI2 Processor Implementation 72                             | 2 |

| 10 | The | BERI Programmable Interrupt Controller 7.                     | 3 |

|    |     | Sources                                                       |   |

|    |     | Source Numbers and Base Addresses on BERI                     |   |

|    |     | Config Registers: PIC_CONFIG_X                                |   |

|    |     | Interrupt-Pending Bits                                        |   |

|    |     | Reset State                                                   |   |

|    |     | Safe Handling of Interrupts                                   |   |

|    |     | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~                        |   |

# Chapter 1

# Introduction

This document is the *BERI Hardware Reference* for the Bluespec Extensible RISC Implementation (BERI) prototype. The document describes the status of the processor prototype and the processor implementations themselves. It provides a reference for various aspects of the hardware platform – such as the BERI Programmable Interrupt Controller (PIC) and supported Altera, Terasic, and Cambridge/SRI IP cores. It complements the *BERI Software Reference*, which describes the BERI software development environment, the *CHERI Instruction-Set Architecture*, which describes the CHERI ISA extensions for fine-grained memory protection and scalable compartmentalization, and the *CHERI User's Guide*, which discusses CHERI-related extensions to the BERI software environment.

### 1.1 Bluespec Extensible RISC Implementation (BERI)

The Bluespec Extensible RISC Implementation (BERI) is a platform for performing research into the hardware-software interface that has been developed as part of the CTSRD project at SRI International and the University of Cambridge. It consists of a CPU supporting the 64-bit MIPS ISA implemented in Bluespec System Verilog and a complete software stack. Supported software packages include the open-source FreeBSD operating system and Clang/LLVM compiler suite. BERI also supports, and broad range of popular open-source applications such as the Apache web server and popular scripting languages. Wherever possible, BERI makes use of BSD- and Apache-licensed software to maximize opportunities for technology transition.

### 1.2 BERI and BERI2 Prototypes

The first BERI prototype (BERI1) was developed between 2010–2014 by Jonathan Woodruff, based in part on an earlier experimental RISC processor created by Gregory Chadwick. We are also developing multi-core support for BERI1. BERI1 is the primary focus of the current *BERI Hardware Reference* and *CHERI User's Guide*.

BERI2 is the second version of the prototype developed between 2011–2014 by Nirav Dave and Robert Norton using a stylized form of Bluespec to better support formal verification. BERI2 is designed to support multi-threaded as well as multi-core operation.

Although BERI and BERI2 share significant infrastructure (for example, memory subsystems and simulated peripheral buses), we do not currently envision convergence of the two

implementations. Instead, we expect researchers to select between BERI1 and BERI2 based on their requirements. BERI1 offers a mature and higher-performance platform for "production" research, such as CHERI, and may be the first port of call for researchers focused on instruction-set and functional extension. BERI2 remains a work in progress as we refine our implementation techniques to better support formal verification, and consider tradeoffs between more performant hardware design techniques and those suitable for verification. In the longer term, we hope that BERI2's support for formal methods tools will lead to much greater correctness and reliability. Its support for hardware multithreading may be of particular interest to researchers interested in scheduling and interthread communication.

## 1.3 The CHERI Capability Model

The first major research project to be implemented on BERI is *Capability Hardware Enhanced RISC Instructions* (CHERI). CHERI is an extension to RISC ISAs to support fine-grained memory protection and scalable protection-domain transition within conventional MMU-based address spaces. Both BERI1 and BERI2 include optionally compiled implementations of the CHERI ISA. To allow use of the CHERI features within UNIX applications, we have developed an extended version of FreeBSD/BERI, called CheriBSD, and made changes to the Clang/L-LVM compiler. These are available under an open-source license, and are described in more detail in the *CHERI Instruction-Set Architecture* and the *CHERI Users' Guide*.

### 1.4 Getting BERI

We distribute the BERI prototype and software stack as open source via the BERI website:

http://www.beri-cpu.org/

## 1.5 Using BERI

The BERI prototype is implemented in the Bluespec System Verilog hardware description language (HDL), which may be compiled into a C-language simulator, or synthesized for an FPGA target. The former requires access to the proprietary Bluespec toolchain; the latter additionally requires access to the Altera FPGA toolchain.

Currently, BERI is supported on the Altera-based Terasic DE4 board. There is also some build infrastructure present for the Altera-based Terasic tPad board, and early support for BERI on the Xilinx-based NetFPGA 10G board.

# 1.6 Licensing

The BERI hardware design, simulated peripherals, and software tools are available under the BERI Hardware-Software License, a lightly modified version of the Apache Software License that takes into account hardware requirements.

We have released our extensions to the FreeBSD operating system to support BERI under a BSD license; initial support for BERI was included in FreeBSD 10.0, but further features will appear in

FreeBSD 10.1. We have also released versions of FreeBSD and Clang/LLVM that support the CHERI ISA under a BSD license; these are distributed via GitHub.

We welcome contributions to the BERI project; however, we are only able to accept non-trivial changes when an individual or corporate contribution agreement has been signed. The BERI hardware-software license and contribution agreement may be found at:

http://www.beri-open-systems.org/

## 1.7 Version History

Some content in this report was previously made available in the CHERI Platform Reference.

- **1.0** The first version of the *Platform Reference Manual* was created from two relocated chapters of the then existing *User's Guide* and new content such as information on the CHERI Programmable Interrupt Controller (PIC), as well as improvements to the peripheral description (such as addition of a boot loader area to the DE4 Intel StrataFlash layout, and information on the Cambridge HDMI controller).

- 1.1 The second version is an incremental update that reflected changes in the CHERI and CHERI2 hardware platforms. Most importantly, the facilities of the new CHERI Floating Point Unit (FPU) are described. This version includes documentation of higher interrupt numbers (available due to the CHERI PIC) for DE4 peripherals. Brief documentation for the Bluespec 6550 UART has been added. The new 64K L1 and L2 caches are documented. Additional divergences from the MIPS R4000 ISA are described, such as the larger 40-bit physical address space. CHERI ISA instruction information is updated. (CSBH, CSWH are no longer defined; CLLD, CSCD are now implemented; BC2F is no longer defined; CBTS, CBTU are now implemented.)

- 1.2 The CHERI Platform Reference has been renamed as the BERI Hardware Reference to reflect its focus on BERI, rather than CHERI. Test-suite attributes and simulator ISA extensions for testing are now documented; test statuses for various parts of the ISA are updated. BERI2 compilation options are now documented. Tables of floating-point instructions, conversions, and rounding modes are now included. Multicore PIC support is now documented. Further ISA extensions for core/thread identification and the thread-local storage register are documented.

- 1.3 UCAM-CL-TR-852 This version of the BERI Software Reference was made available as a University of Cambridge Technical Report. This version attempts to reduce the degree to which instructions and information (e.g., Subversion repository location) are dependent on the SRI/Cambridge development environment; build documentation has generally been improved. The instructions for simulating BERI were expanded to cover setting up a development environment from scratch including obtaining all the tools. Information was updated to reflect open sourcing of BERI/CHERI and its software stack. Numerous general updates are made to reflect ongoing BERI development, including a transition from virtually to physically indexed L1 caches. Instruction and coprocessor status information is updated: CACHE instruction operations are now listed; supported CP0 registers are listed; implementation-defined registers are documented. BERI1 and BERI2 are now better differentiated throughout the document. Support for the Terasic tPad is deemphasized in favor of the Terasic DE4. Testing documentation has been updated to describe the test-suite support library, as well as multi-threaded testing support. FPU implementation status has been updated. The chapter order was changed to have a more logical flow.

### 1.8 Document Structure

This document is an introduction to and reference manual for the BERI processor prototype in simulation, and synthesized for Altera FPGAs on Terasic boards.

Chapter 2 documents how to check out the BERI source code, build the BERI simulator, and run the BERI unit test suite. Various build options are discussed, including debug options.

Chapter 3 describes the BERI hardware debug unit, which allows low-level access to processor internals via a real or simulated UART, for the purposes of debugging.

Chapter 4 documents the BERI unit test suite, including how to run the suite and add new tests.

Chapter 5 describes how to configure and synthesize BERI in the Altera development environment.

Chapter 6 describes how to build and synthesize the BERI prototype for the Terasic DE4 FPGA development board and Terasic tPad FPGA teaching board.

Chapter 7 describes the instruction-set architecture implemented by the BERI prototypes, including 64-bit MIPS and CHERI instructions. In particular, it documents sections of the MIPS ISA that have been intentionally omitted (e.g., 32-bit compatibility; mixed-endian support). It also documents the implementation status of BERI-specific ISA features, as well as aspects of the configuration of reference BERI systems such as physical memory maps.

Chapter 8 provides a high-level description of the BERI1 implementation.

Chapter 9 provides a high-level description of the BERI2 implementation.

Chapter 10 describes the BERI Programmable Interrupt Controller, an integrated device that supports interrupts from peripherals as well as interprocessor interrupts (IPIs). The PIC is also responsible for mapping a larger number of interrupt sources associated with peripherals down to a smaller number of processor interrupt lines.

# Chapter 2

# **Simulating BERI**

This chapter describes how to check out the BERI source code, build the BERI simulator, and run the BERI unit test suite. It describes various build targets for the simulator with varying levels of tracing. This documentation assumes access to the following resources:

- 64-bit Ubuntu Linux 14.04 LTS workstation (32-bit and 64-bit Ubuntu Linux 10.04.2 LTS and 12.04 LTS workstation and server have worked in the past). Other distributions may work with some changes to this workflow: we suggest running in an Ubuntu virtual machine to begin with.

- Either a public release of BERI, or the private Subversion repository containing the current development version.

### 2.1 Software Dependencies to Build BERI

### 2.1.1 Installing Bluespec System Verilog compiler

This release is tested with version 2014.05.C of the Bluespec compiler. Access to the Bluespec compiler requires a license from Bluespec. If you are an academic institution you can sign up to the University Program at:

```

http://bluespec.com/university-program.html

```

Bluespec requires you to configure a FlexLM license server and will supply you with instructions for installing the software. Specific releases of Bluespec can be downloaded from the Software Releases section of the Bluespec Forum (you need to be logged in to see the attachments):

```

http://www.bluespec.com/forum/

```

### 2.1.2 Ubuntu Package Dependencies

Table 2.1 documents Ubuntu packages required to build the BERI simulator and test suite. To install an Ubuntu package such as those listed in the table, using the following command:

```

sudo apt-get install <package-name>

```

| Program         | Ubuntu Package  | Required to                     |

|-----------------|-----------------|---------------------------------|

| Subversion      | subversion      | Check out                       |

| Git             | git             | Check out                       |

| Build tools     | build-essential | C compiler and libraries        |

| GNU make        | make            | Build, run test suite           |

| GNU Bison 2.4.1 | bison           | Build simulator                 |

| bzip2           | bzip2           | Uncompress tarballs             |

| Flex 2.5.35     | flex            | Build simulator                 |

| Perl            | perl            | Build                           |

| Python 2.6      | python          | Build, run test suite           |

| SDL 1.2.14      | libsdl1.2-dev,  | Build, run simulated tPad frame |

|                 | libsdl1.2debian | buffer                          |

| Nose 0.11.1     | python-nose     | Run test suite                  |

Table 2.1: Software build dependencies for BERI components

### 2.1.3 Installing the GCC Compiler

BERI requires a MIPS cross compiler. We use the gcc-4.4-mips-linux-gnu package from Emdebian. A script to install the compiler on Ubuntu 14.04 may be found in the BERI source distribution here:

```

cheri/trunk/install-mips-gcc.sh

```

Please be aware that these packages come from a non-system repository and this script will add this and the standard Debian repository to your system configuration. It will attempt to minimise the number of packages installed from Debian. This step will also install a necessary dependency (the libgmp3c2 package) for Bluespec.

### 2.1.4 Installing the CHERI MIPS assembler

The CHERI MIPS assembler extends the GNU assembler with additional capability support, and is available from:

```

https://github.com/CTSRD-CHERI/binutils

```

You can build this with:

```

git clone https://github.com/CTSRD-CHERI/binutils

cd binutils

./configure --target=mips64 --disable-nls --disable-werror

make

sudo make install

```

### 2.1.5 Installing the Altera Quartus II FPGA tools (optional)

To build BERI for Altera FPGAs, you will need to install the Quartus II FPGA tools. This version of BERI is tested with Quartus II version 13.1 subscription edition, which will need a license from

Altera. It may work with the free Quartus II web edition, but we have not tested this. Quartus II can be downloaded from:

```

http://www.altera.com/

```

If you do not wish to download the full package you need to download the Quartus II Software bundle (about 1.8GB) and the device support for the Stratix IV (630MB) if targeting the DE4 platform. We recommend accepting the default installation options.

### 2.2 Extracting a BERI Release

BERI releases are distributed as compressed tarballs suitable for extraction and use on UNIX. You can extract the tarball using:

```

tar -xjf cheri-rXXXXX.tbz

```

Where rxxxxx reflects the Subversion revision used to create the release. You will then have a source distribution containing high-level directories:

```

cheri/trunk BERI1 cheri2/trunk BERI2

```

cheribsd/trunk Boot loaders and scripts

cherilibs/trunk BERI1/BERI2 common code and tools

cheritest/trunk BERI test suite

You will also find a README file and information on copyright and licensing.

## 2.3 Checking Out the Development Version of BERI

Alternatively, if you have access to the CTSRD Subversion repository, the following instruction will allow you to check out the BERI source code.

The Cambridge Subversion repository uses SSH authentication keys as capabilities to identify the repository and rights held by a client. By default, SSH will offer keys held by the agent (or in your home directory) in the order it finds them, which, if you hold multiple keys to different repositories on the Subversion server, may cause SSH to select the wrong key. It is therefore necessary to ensure that the right SSH key is used. One way to do so is to create a new SSH agent, adding only the appropriate key to that session<sup>1</sup>. To set up an SSH agent in this manner, use something like the following:

```

ssh-agent bash

ssh-add ~/.ssh/id_ctsrd_rsa

```

It is also possible to configure .ssh/config to offer only a specific key to specific servers; see the SSH man page for details. To perform an initial checkout of BERI, use the following Subversion command:

```

svn co svn+ssh://secsvn@svn-ctsrd.cl.cam.ac.uk/ctsrd ctsrd

```

To update an existing checkout of BERI, use the following Subversion command:

```

cd ctsrd svn update

```

$<sup>^{1}</sup>$ On Mac OS X, new ssh-agent sessions inherit all SSH keys added to the user keychain, so you must run ssh-add  $^{-}$ D to flush them. This step is not required on other platforms.

### 2.4 Configuring the Build Environment

The BERI source code and build tools may be found in the cheri/trunk directory tree (or for BERI2, cheri2/trunk). Before building BERI, you must configure the Bluespec development environment:

```

cd cheri/trunk

cp setup-local-example.sh setup-local.sh

```

Next, edit setup-local.sh to point to your local install of Bluespec (and Quartus, if available). You should only need to change the first few lines of this file. You can test your install with:

```

cd cheri/trunk

source setup.sh

bsc -v

quartus sh -v

```

Whenever you run a BERI build or run you need to source setup. sh to add these tools to your path. You must be in the cheri/trunk directory when you source this script.

### 2.5 Building the BERI Simulator

The BERI build is sensitive to a number of make variables, depending on which components should be included or excluded from the pipeline. A typical run of the simulator might be initiated using:

```

make sim CAP=1

./sim

```

The BERI build is configured using five make variables; these are shown in Table 8.3.

MICRO Cause BERI to build without an L2 cache or virtual-address translation.

NOBRANCH Do not predict branches; always wait for the final branch destination before fetching the next PC.

CAP Include the CHERI capability unit.

COP1 Build with the Floating-Point Unit (FPU).

COP3 Build with the experimental general-purpose coprocessor 3.

The BERI executable is sensitive to four arguments. The +trace argument will give a concise report for each instruction committed. The +cTrace argument will report the number of dead cycles between committed instructions. The +regDump argument will enable the debug instructions which report the contents of the register files. The +debug argument will report all debug output from the internal processor state.

The build also compiles an interactive software test tool, found in the sw sub-directory. The simulation can also be used to run the CHERI test suite described in Chapter 4, and to boot OS images (e.g., FreeBSD) using the simboot loader found in cheribsd/trunk/simboot. When the simulator is run, it loads a memory image from the current working directory; running the simulator from the root of the BERI development tree will automatically load the interactive test tool.

### 2.6 Configuring the BERI Simulator

At startup, the simulator tries to read the file ./simconfig or the file pointed to by the environment variable CHERI\_CONFIG. This file describes in a C-like syntax how the hardware should be simulated. A valid configuration must exist or the simulator will not start. A default configuration file is included in the cheri/trunk directory.

Individual simulated hardware peripherals are built as shared libraries. The simulator will attempt to dlopen() these shared libraries as they are encountered in the configuration file. Any module-specific options are passed to the module at load-time. If a module fails to load, either because it cannot be found or because invalid options were given, the simulation will terminate with an assertion failure. Figure 2.1 illustrates a sample simconfig file.

First, a series of simulated device modules are loaded using module statements; paths must be specified. Then, a series of devices is declared using device blocks, which must each declare a class, which selects the simulated device type; for each device, at least a base address (addr) and length (length) must be specified. An optional irq can be set, as well as device class-specific parameters such as socket types, file paths, and so on. Devices can be conditionally defined based on whether environmental variables have been set; both positive ifdef and negative ifndef syntaxes are permitted. Finally, options can be set from environmental variables using the getenv syntax; if a variable is not set, then an empty string will be used for the value.

### 2.7 Simulating BERI

When the sim target is used, a simulator binary, sim, is generated. The simulator automatically loads a physical memory image from a series of hex memory files, mem0.hex, mem1.hex, ... mem7.hex, used to populate initial memory contents for BRAM. By default, the memory image generated from sw contains a small interactive test suite that communicates via a simulated serial I/O hooked up to the simulator's standard input and output streams.

### 2.8 Running the BERI Test Suite

The cheritest/trunk subtree contains a MIPS ISA unit test suite that exercises various processor features, including initial register values, memory access, jump instructions, exceptions, and so on. make test in the cheritest/trunk tree will run the test suite; a detailed discussion of the test suite appears in Chapter 4.

```

module ../../cherilibs/trunk/peripherals/dram.so

module ../../cherilibs/trunk/peripherals/ethercap.so

module ../../cherilibs/trunk/peripherals/uart.so

device "dram0" {

class dram;

addr 0x0;

length 0x40000000;

} ;

ifdef "CHERI_KERNEL" device "kernel" {

class dram;

addr 0x100000;

length 0xff00000;

option path getenv "CHERI_KERNEL";

option type "mmap";

option cow "yes";

};

ifdef "CHERI_SDCARD" device "sdcard0" {

class sdcard;

addr 0x7f008000;

length 0x400;

option path getenv "CHERI_SDCARD";

option readonly "yes";

} ;

ifndef "CHERI_CONSOLE_SOCKET" device "uart0" {

class uart;

addr 0x7f000000;

length 0x20;

irq 0;

option type "stdio";

ifdef "CHERI_CONSOLE_SOCKET" device "uart0" {

class uart;

addr 0x7f000000;

length 0x20;

irq 0;

option type "socket";

option path getenv "CHERI_CONSOLE_SOCKET";

}

```

Figure 2.1: Example simconfig configuration file

# Chapter 3

# **Using the BERI1 Debug Unit**

The BERI1 prototype includes a simple debug unit that communicates with an external host using a two-way streaming 8-bit interface. The debug unit can pause and step the pipeline, set breakpoints, and insert instructions into the pipeline. Instructions inserted by the debug unit may use operands from the debug unit as well as operands from the register file. The result of an instruction from the debug unit may be written back to the debug unit as well as the register file. These debug unit elements may be used to implement a variety of higher-level services, including a proxy from the GDB server protocol, and an external memory image loader. In general, users of BERI should interact with the debug unit using berictl rather than interfacing directly with the debug-unit protocol, which is subject to change over time and between BERI versions.

### 3.1 Communicating with the BERI Debug Unit

The BERI debug unit communicates with a host computer over a two-way streaming 8-bit interface. The current system uses an Altera JTAG streaming component which is tunnelled over USB to the host PC; berictl can use the same protocol over a UNIX domain socket to communicate with a simulated debug unit. The Altera System Console utility may send and receive bytes to and from the debug unit using a desktop computer connected with a USB cable. All commands and responses are defined as series of bytes sent or received over this streaming channel.

Commands and responses traveling over the channel are arranged as messages. Every message begins with two bytes. The first is the message type and the second is the message length. If the message length is non-zero, the prescribed number of bytes follow the two bytes of the message header.

## 3.2 BERI Debug Registers

The BERI debug unit has eight registers:

- Debug Instruction

- · Operand A

- Operand B

- Breakpoint 0

- Breakpoint 1

- Breakpoint 2

| Instruction                | Command | Length | Payload        |

|----------------------------|---------|--------|----------------|

| Load Instruction           | i       | 4      | Instruction    |

| Load Operand A             | a       | 8      | 64-bit Operand |

| Load Operand B             | b       | 8      | 64-bit Operand |

| <b>Execute Instruction</b> | e       | 0      |                |

| Report Destination         | d       | 0      |                |

| Load Breakpoint 0          | 0       | 8      | 64-bit Address |

| Load Breakpoint 1          | 1       | 8      | 64-bit Address |

| Load Breakpoint 2          | 2       | 8      | 64-bit Address |

| Load Breakpoint 3          | 3       | 8      | 64-bit Address |

| Pause Execution            | p       | 0      |                |

| Resume Execution           | r       | 0      |                |

| Step Execution             | S       | 0      |                |

| Resume Execution           | r       | 0      |                |

| Move PC to Destination     | c       | 0      |                |

| Resume Unpipelined         | u       | 0      |                |

Table 3.1: Instruction messages for the debug unit

- Breakpoint 3

- Destination

The first seven registers can be written and the Destination register can be read.

## 3.3 BERI Debug Instructions

The BERI debug unit supports the instructions listed in Table 3.1. The "Command" is the ASCII character that should appear in the first byte of the message sent to the debug unit, that is, the message type. The "Length" is the value of the second byte of the message. The "Payload" is the contents of the following bytes, equal in number to the value of the "Length" field. All instructions will produce a response from the debug unit confirming completion of the request. These message types are listed in Section 3.4.

#### **Notes on Some Instructions:**

**Load Instruction** Load an instruction into the debug unit's Instruction register in preparation for inserting it into the processor pipeline.

**Load Operand A & B** Load values into the Operand A & B registers for possible use as operands of the instruction in the Instruction register.

**Execute Instruction** Insert the instruction contained in the Instruction register into the processor pipeline.

| Message                         | Type Byte | Length | Payload             |

|---------------------------------|-----------|--------|---------------------|

| Load Instruction Response       | 0xe9      | 0      |                     |

| Load Operand A Response         | 0xe1      | 0      |                     |

| Load Operand B Response         | 0xe2      | 0      |                     |

| Execute Instruction Response    | 0xe5      | 0      |                     |

| Execute Exception Response      | 0xc5      | 1      | MIPS Exception Code |

| Report Destination Response     | 0xe4      | 8      | 64-bit Value        |

| Load Breakpoint 0 Response      | 0xb0      | 0      |                     |

| Load Breakpoint 1 Response      | 0xb1      | 0      |                     |

| Load Breakpoint 2 Response      | 0xb2      | 0      |                     |

| Load Breakpoint 3 Response      | 0xb3      | 0      |                     |

| Pause Execution Response        | 0xf0      | 0      |                     |

| Resume Execution Response       | 0xf2      | 0      |                     |

| Step Execution Response         | 0xf3      | 0      |                     |

| Resume Execution Response       | 0xf2      | 0      |                     |

| Move PC to Destination Response | 0xe3      | 0      |                     |

| Resume Unpipelined Response     | 0xf5      | 0      |                     |

| Breakpoint Fired                | 0xff      | 8      | 64-bit Address      |

Table 3.2: Message types from the debug unit

**Report Destination** Report the 64-bit (8-byte) value in the Destination register. The debug unit will send a message containing the contents of the Destination register back to the debugger.

**Step Execution** Step one instruction if the processor is paused. If the next instruction is a branch, the branch delay slot and the branch target will also be executed.

Accessing Debug Registers from Debug Instructions When instructions originate from the debug unit, references to R0 are interpreted as references to registers in the debug unit. An instruction from the debug unit which takes two operands from R0 and writes back to R0 will take Operand A and Operand B and will write back to the Destination register in the debug unit. In general, if "rs" refers to R0, that operand will come from Operand A in the debug unit and if "rt" refers to R0, that operand will come from Operand B in the debug unit.

### 3.4 BERI Debug Responses

Table 3.2 lists message types that the debug unit may generate. All of them are direct responses to instructions except for the "Breakpoint Fired" command which might be delivered at any time.

#### **Notes for Some Responses:**

**Execute Instruction and Exception Responses** When an "Execute Instruction" command is received, the debug unit will return an "Execute Instruction Response" message if execution of the instruction did not throw an exception. If the instruction generated an exception, the debug unit will return an "Execute Exception Response" message with a payload of one byte which will contain the 5-bit MIPS exception code generated by the instruction.

**Breakpoint Fired** The "Breakpoint Fired" message is sent when an instruction commits a next PC in write-back which is equal to one of the four breakpoint registers. The "Breakpoint Fired" message has a payload containing the 8-byte address value of the breakpoint that fired.

# **Chapter 4**

# The BERI Unit Test Suite

The BERI prototype includes a simple unit test suite implemented using the Python Nose framework. The test suite exercizes key BERI functionality in a controlled and easily diagnosable environment, an instrumented BERI simulator, with a goal of testing both basic MIPS ISA functionality and CHERI security extensions. This chapter explains the structure and components of the test suite, how to run the test suite, and how to add new tests. It also describes some of the tools available for diagnosing test results.

### 4.1 The BERI Unit Test Environment

The BERI unit test suite is implemented using a combination of the BERI Bluespec simulator (with extensions for debugging), make, the MIPS toolchain, the Python Nose test framework, and a moderate collection of test programs and Nose classes to evaluate test output. The unit test suite can also be run against the gxemul MIPS simulator, which has proven useful for checking our interpretation of the MIPS ISA against a more common interpretation. In the future, we hope also to run the test suite against BERI synthesized in an FPGA, likely with the help of JTAG.

### 4.2 Software Dependencies

To run the BERI unit test suite, you will need to have the following software installed:

- Python

- The MIPS GCC cross-linker, installed as mips-linux-gnu-ld.

- The CTSRD-modified version of the GNU binutils, available from:

```

https://github.com/CTSRD-CHERI/binutils

```

The assembler should be installed as mips64-as, objcopy as mips64-objcopy and so on.

If you want to run the tests that are written in the C language with capability extensions, you will also need the CTSRD-modified version of the Clang compiler, available from:

```

https://github.com/CTSRD-CHERI/llvm

```

If you want to run the tests against GXEMUL, you will also need the CTSRD-modified version of GXEMUL, available from:

| Directory        | Description                                     |

|------------------|-------------------------------------------------|

| cheritest/trunk/ | Root of the BERI test suite tree, home of the   |

|                  | makefile, linker scripts, and test library code |

| gxemul_log/      | Destination for gxemul test run output          |

| log/             | Destination for BERI simulator test run output  |

| obj/             | Destination for test object files, memory       |

|                  | images, and assembly dumps                      |

| tests/           | Various subdirectories holding source code      |

|                  | for individual tests, and their matching Python |

|                  | Nose classes                                    |

| tools/           | Utility functions to perform common func-       |

|                  | tions such as interpreting BERI simulator and   |

|                  | gxemul output                                   |

| fuzzing/         | Scripts for fuzz testing the TLB                |

Table 4.1: Directories in the BERI unit test suite

https://github.com/CTSRD-CHERI/gxemul

The modified GXEMUL does not include support for the capability instructions, but it does include modifications to integrate it with our test framework, and improved emulation of floating point instructions.

If you want to run the tests against the formal model of MIPS ISA developed by the REMS ("Rigorous Engineering for Mainstream Systems") project, you will also need their MIPS ISA formal model, available from:

```

http://www.cl.cam.ac.uk/~acjf3/13

```

You will also need REMS project's support libraries to turn the model into an executable specification: they are available from:

```

http://www.cl.cam.ac.uk/~acjf3/13/13mips.tbz2

```

If you want to run the tests against a Bluespec-level simulation of BERI, you will also need the Bluespec tools, and a compatible version of GCC. (Bluespec is compiled into C++ which is then compiled by g++).

### **4.2.1** BERI Test-Suite Directory Layout

Table 4.2.1 describes the directories in the BERI unit test suite.

### 4.2.2 BERI ISA Extensions for Testing

The BERI test suite employs debugging extensions to the 64-bit MIPS ISA to examine the state of a simulated BERI system after each test. It dumps the general-purpose register file, the CP0 registers and the capability coprocessor registers, and allows tests to terminate the simulation in a controlled manner. Current extensions are exposed via CP0 register operations, as shown in Table 4.2. In the future they will likely move to capability coprocessor extensions to reduce the possibility of collision with the existing MIPS ISA. In the future, we anticipate the addition of further extensions in support of testing to dump the simulation memory image.

| Instruction                                  | Description                                                  |

|----------------------------------------------|--------------------------------------------------------------|

| mtc0 register, \$26                          | Dump arithmetic registers to trace                           |

| mtc0 register, \$26, 1 mtc2 register, \$0, 6 | Dump ICache tags to trace Dump capability registers to trace |

| mtc0 register, \$23                          | Stop the simulation                                          |

Table 4.2: BERI ISA extensions for testing

### **4.2.3** Unit Test Support Library

Most BERI unit tests are linked against a thin loader, init.s, which is responsible for setting up various aspects of CPU and memory configuration. They serve to:

- Set up a stack at the top of memory.

- Install default before- and after-boot exception vectors and handlers, which will dump the register file and terminate if triggered.

- Explicitly clear all general-purpose registers except stack-related registers that may have been modified during startup.

- Invoke a user-provided test function using JAL; currently all test functions are implemented in assembly, but the calling convention should support C as well.

- On return from test, dump the register file and terminate.

In addition, a small library of support routines (including functions for copying memory and installing exception handlers) that are common to more complex tests may be found in lib.s. We anticipate that this library will grow in size as the test suite is made more comprehensive.

A few low-level tests, referred to as *raw tests*, execute directly rather than via init.s, and are not linked against lib.s. Raw tests perform low-level verification of CPU functionality required to reliably run init.s, such as initial register file values on CPU reset, arithmetic instructions, the reliability of branch and jump instructions, and basic memory operations. Whenever possible, writing raw tests should be avoided, because they necessarily replicate functionality (such as register dumping), and lack access to a pre-configured stack.

Note that all tests will be run twice by the suite – once from uncached instruction memory, and once from cached instruction memory. Timing and pipeline effects differ significantly between the two cases. One impact of this difference is that all tests must be relocatable and able to run in multiple MIPS xkphys segments.

## 4.3 Running the BERI Test Suite

Typically, the test suite will be run as follows:

```

$ cd cheritest/trunk

```

\$ make test

The CHERIROOT variable may be used to tell the test suite where to find BERI tools for processing memory images and the BERI simulator; the BERI simulator must first have been built using make sim or similar. The test suite may be run against gxemul as follows:

| TRACE       | Include per-instruction tracing in log files |

|-------------|----------------------------------------------|

| CHERI_MICRO | Don't run TLB tests                          |

| NOFUZZ      | Don't run TLB fuzz tests                     |

| COP1        | Run floating point tests                     |

| TEST_CP2    | Run capability unit test                     |

| CLANG       | The Clang compiler supports capabilities     |

| MULTI       | Run multi-core tests                         |

| MT          | Run multi-threaded tests                     |

| CHERI_VER   | Version of BERI to test (default 1)          |

Table 4.3: Environment variables for the test suite

```

$ cd cheritest/trunk

$ make gxemul-build

$ make gxemul-nosetest

$ make gxemul-nosetest_cached

```

The test suite can be configured to run only a subset of the tests, by setting the environment variables shown in Table 4.3. TEST\_CP2 and CLANG default to 1, so the capability tests will be run unless they are set to 0. Some tests check the behavior of FPU instructions in a CPU without an FPU; they should raise a reserved instruction exception. These these tests will fail if TEST\_FPU is not set and the CPU under test has been configured with a FPU.

By default, the test will run against the BERI1 simulator in . . / . . /cheri/trunk. If CHERI\_VER is set to 2, tests will be run against BERI2 instead.

#### **4.3.1 Jenkins**

If you are developing in the Cambridge development environment, the BERI unit test suite is run automatically by the Jenkins build framework. Jenkins can be monitored by visiting the following URL:

```

https://ctsrd-build.cl.cam.ac.uk

```

### 4.4 Unit Test Structure

Each unit test consists of a short assembly program that exercizes specific features in the BERI CPU, and a Nose class that contains a set of assertions about termination state for the test. Modifications to the test suite typically take the form of modifying an existing test to check new assertions, or adding an entirely new test via a new test program and set of corresponding assertions.

### 4.4.1 Test Types

Tests are split into two categories: raw tests that have few low-level dependencies and are intended to exercise basic CPU features such as the register file, and higher-level tests that are able to depend on common CPU initialization code and a support library. Raw tests are necessarily run before higher-level tests, which typically depend on features checked in raw tests. Raw test files are prefixed with raw\_, and higher-level test file names are prefixed with test\_; the build framework uses these prefixes to identify assembly and linking requirements, so they must be used.

Unless there is a specific reason to do so, new tests should be added as higher-level tests, relying on the init.s framework to set up the stack, dump register state on completion, and terminate the simulator, rather than hand-crafting this code. This provides access to routines such as memcpy that are frequently useful when implementing tests.

#### 4.4.2 Test Structure

All tests are compiled using 64-bit MIPS instructions, and attempt to follow a standard application binary interface (ABI) to allow easy reuse of compiled MIPS code reused in the test environment. Currently, no C code is linked into the test suite; however, it is easy to imagine doing so in the future – in which case ABI conformance would be critical.

High-level tests implement a single, global function test. When test terminates, the calling code in init.s will dump register state and terminate the simulator; these registers then become available to the Nose test framework for checking. Other than changes to the program counter, **\$PC**, the test framework avoids any changes to register values after the test returns. Tests may rely on the availability of a roughly 1K stack. Tests execute in both the cached but unmapped region of memory around  $0 \times 9800000040000000$ , with a stack growing down from  $0 \times 980000000800008000$ , and the uncached and unmapped region around  $0 \times 900000000000$ , with a stack growing down from  $0 \times 9000000080000000$ , but may make use of any required processor features such as cached and mapped memory regions, CP0 MMU operations, etc.

#### 4.4.3 Test Termination

Normally, high-level tests will terminate by returning from the test function, triggering a register dump and simulator termination. However, the test framework is executed with a 100000-cycle limit on simulation time in order to ensure termination, catching (for example) infinite loops in software, or exception cycles. As tests become more complicated, this limit may need to be changed; currently, its presence ensures that tests will eventually always terminate, even if software enters an infinite loop.

### 4.4.4 Connecting New Tests to the Build

Nose test files must begin with the prefix test\_, which will normally occur for high-level tests; Nose test files for raw tests will therefore be prefixed with test\_raw\_. New unit tests are hooked up to the build system by adding their source files to the TEST\_FILES variable in the makefile. This is normally done by adding the test filename to one of the make variables for a test subset such as TEST\_ALU\_FILES. For the time being, all test source and Nose files must be placed under the tests directory in an appropriate sub-directory which should be included in the TESTDIRS variable.

#### 4.4.5 Test Attributes

Each of the Python test scripts is tagged with Python attributes that indicate which versions of BERI (or generic MIPS) the test is expected to run on. The default (no attributes) is that the test is expected to work on any processor that complies with the MIPS R4000 ISA specification. Dependencies on additional features are indicated by using the attributes show in Tables 4.4 and 4.5.

| Attribute       | Description                                    |

|-----------------|------------------------------------------------|

|                 |                                                |

| beri            | Test depends on BERI implementation details    |

| beriinitial     | Initial values of registers same as BERI       |

| cache           | CPU has cached memory                          |

| cached          | Test must be run from cached memory            |

| capabilities    | CHERI capability unit                          |

| comparereg      | CP0 Compare register                           |

| config3         | CP0 Config3 register                           |

| counterdev      | Counter device                                 |

| dumpicache      | Write to CP0 reg 26, sel 1 dumps the ICache    |

| ignorebadex     | 32-bit arithmetic ignores the top 32 bits      |

| invalidateL2    | CACHE instruction for L2 cache                 |

| llsc            | Load-linked and store conditional instructions |

| llscnotmatching | SC will fail if address doesn't match LL       |

| llscspan        | SC succeeds even if there is a load after LL   |

|                 | SC fails if there is a store after LL          |

| lladdr          | CP0 LLAddr register                            |

| rdhwr           | RDHWR instruction                              |

| swi             | Software interrupts                            |

| tlb             | Translation lookaside buffer                   |

| smalltlb        | A TLB just like CHERI2's                       |

| bigtlb          | A TLB just like CHERI1's                       |

| gxemultlb       | A TLB just like GXEMUL's                       |

| largepage       |                                                |

| mt              | Multi-threaded CPU                             |

| mtc0signex      | MTC0 sign-extends the value moved              |

| nofloat         | Test will only work if FPU is absent           |

| trapi           | TRAPI instruction                              |

| userlocal       | User local register                            |

| watch           | Watch points                                   |

Table 4.4: Test attributes

| Attribute      | Description                                     |

|----------------|-------------------------------------------------|

| float          | Floating point unit                             |

| float32        | Floating point unit that supports 32-bit mode   |

| float64        | Floating point unit that supports 64-bit mode   |

| floatcmove     | Floating point conditional move instructions    |

| floatexception | Floating point unit can raise exceptions        |

| floatflags     | FPU supports IEEE condition flags               |

| floatfcsr      |                                                 |

| floatfexr      |                                                 |

| floatfenr      |                                                 |

| floatindexed   |                                                 |

| floatpaired    | Floating point unit that supports paired single |

| floatrecip     | RECIP.D and RECIP.D instructions                |

| floatrsqrt     | RSQRT.S and RSQRT.D instructions                |

Table 4.5: Additional attributes for floating point tests

# 4.5 Unit Test Support Library

All tests (apart from the "raw" tests) are linked against the subroutine library lib.s. The subroutines defined in lib.s are as follows:

#### **Copying Memory**

```

void *memcpy(void *dest, const void *src, int n);

```

memcpy () behaves as defined in ANSI C. It copies n bytes from src to dest, and returns the value of dest.

#### **Exceptions**

```

void bev_clear(void);

```

bev\_clear() clears the BEV bit in the CPO status register, so that subsequent exceptions will use the bev0, rather than bev1, transfer vectors.

```

void install_bev0_stubs(void);

```

For each type of exception, <code>install\_bev0\_stubs()</code> copies a stub subroutine its bev0 handler address. The stub subroutine just loads a pointer to an exception handler from a memory address, and jumps to it. The stub subroutine may not work correctly if CHERI extensions are being used and <code>PCC.base</code> is non-zero; tests that use capabilities may need to provide their own stub.

```

void install_bev1_stubs(void);

```

$\verb|install_bev1_stubs()| does the same thing as \verb|install_bev0_stubs()|, except it copies the stub subroutine to the bev1 exception handler addresses.$

```

void set_bev0_tlb_handler_(void *handler);

void set_bev1_tlb_handler_(void *handler);

void set_bev0_xtlb_handler_(void *handler);

void set_bev1_xtlb_handler_(void *handler);

void set_bev0_cache_handler_(void *handler);

void set_bev1_cache_handler_(void *handler);

void set_bev0_common_handler_(void *handler);

void set_bev1_common_handler_(void *handler);

```

These functions set the address of the exception handler that the stub subroutines will jump to. This handler needs to be written in assembler, not C, as registers are not initialized to follow the C ABI before it is invoked – rather, registers except for \$k0 will have whatever value they contained at the time the exception was triggered; \$k0 is used as workspace by the stub subroutine.

```

void bev0_handler_install(void *handler);

Calls bev0_install_stubs() and set_bev0_common_handler().

void bev1_handler_install(void *handler);

Calls bev1_install_stubs() and set_bev1_common_handler().

```

#### **Assertions**

```

#include "assert.h"

void __assert_line(int line);

void assert(int cond);

```

\_\_assert\_line() terminates the simulation, storing line in register \$v0. Tests written in the C language should return 0 on successful completion of the test; thus, the test framework can tell whether the test failed by examining the final value of \$v0.

assert () is a C macro that will call assert\_fail () with the current line number if cond is zero. In a C language test, it can be used to report a failure if part of the test has failed.

### 4.5.1 Multithreading

```

int get_thread_id(void);

```

Returns the ID of the hardware thread on which it is running.

```

int get_max_thread_id(void);

```

Returns the maximum hardware thread ID (one less than the maximum number of threads).

```

int get_core_id(void);

```

Returns the ID of the core on which it is running.

```

int get_max_core_id(void);

```

Returns the maximum core ID (one less than the number of cores).

```

void thread_barrier(char *barrier);

```

thread\_barrier is used to synchronize all the hardware threads of the CPU. The parameter is a character array with one element for each thread; in assembly language, this array can be allocated with the mkBarrier macro. If a thread calls thread\_barrier, it will block until all other threads have also called thread\_barrier with the same parameter.

```

void other_threads_go(void);

```

other\_threads\_go is equivalent to thread\_barrier (reset\_barrier). The parameter is a static variable declared in init.s). Run at the beginning of all non-raw tests, init.s will cause all threads apart from thread zero to block on reset\_barrier. A single-threaded test can leave the other threads blocked for the duration of the test. In a multi-threaded test, thread 0 (the only thread running at the start) can start all the other threads running by calling other\_threads\_go, releasing them from the barrier. The other threads should not call other\_threads\_go, as that would cause them to be blocked on reset\_barrier subsequently.

### 4.6 Example Unit Test: Register Zero

To explore the above design, we will consider the test\_reg\_zero unit test, which checks that the MIPS general-purpose register **R0**, also known as **\$zero**, has the required special property that it always return the value 0. The correct functioning of **\$zero** is not required for any raw tests, nor init.s, so the test is placed in the high-level test suite. The test performs a number of activities:

- Sets up a stack for the function test by manipulating \$sp and \$fp.

- Pushes the return address, \$ra, and saved frame pointer, \$fp, onto the stack.

- Copies a value from **\$zero** into **\$t0** for inspection.

- Assigns a value to **\$zero** from an immediate, and then copies out to **\$t1** to confirm that the value does not get saved.

- Assigns a value to **\$zero** from a register, and then copies out to **\$t2** to confirm that the value does not get saved.

- Restores **\$fp** and **\$ra** from the stack and returns.

### 4.6.1 Register Zero Test Code

Example assembly source code is illustrated in Figure 4.6.1.

### 4.6.2 Register Zero Nose Assertions

Figure 4.6.2 illustrates the Nose assertion set for this test, confirming a number of desired properties that should hold after the test code runs:

- that **\$zero** held zero on exit,

- that \$t0 held zero on exit, meaning that a simple move from \$zero held zero on start,

- and that registers \$t1 and \$t2 held zero values, meaning that various writes to \$zero did not change the value returned when reading the register.

```

.set mips64

.set noreorder

.set nobopt

.set noat

# This test checks that register zero behaves the way it should: each of

\# $t0, $t1, and $t2 should be zero as at the end, as well as $zero.

.global test

test: .ent test

daddu \$sp, \$sp, -32

sd $ra, 24($sp)

sd $fp, 16($sp)

daddu $fp, $sp, 32

# Pull an initial value out

move $t0, $zero

# Try storing a value into it from an immediate

li $zero, 1

move $t1, $zero

# Try storing a value into it from a temporary register

li $t3, 1

move $zero, $t3

move $t2, $zero

ld $fp, 16($sp)

ld $ra, 24($sp)

daddu $sp, $sp, 32

jr $ra

nop # branch-delay slot

.end test

```

Figure 4.1: Example regression test checking properties of **\$zero**

```

from beritest_tools import BaseBERITestCase

class test_reg_zero(BaseBERITestCase):

def test_zero(self):

'''Test that register zero is zero'''

self.assertRegisterEqual(self.MIPS.zero, 0,

"Register zero has non-zero value on termination")

def test_t0(self):

'''Test that move from zero is zero'''

self.assertRegisterEqual(self.MIPS.t0, 0,

"Move from register zero non-zero")

def test_t1(self):

'''Test that immediate store of non-zero to zero returns zero'''

self.assertRegisterEqual(self.MIPS.t1, 0,

"Immediate store to register zero succeeded")

def test_t2(self):

'''Test that register store of nonzero to zero returns zero'''

self.assertRegisterEqual(self.MIPS.t2, 0,

"Register move to register zero succeeded")

```

Figure 4.2: Example Nose assertion file for the **\$zero** test

### 4.7 Conclusion

This chapter introduces the BERI unit test suite. It explores both the structure of the suite and the implementation of individual tests. The test suite is intended to supplement formal methods by testing the programmer-level view of ISA correctness. While it cannot be authoritative regarding the correctness of BERI, it is extremely valuable in development, because it exercises critical instruction combinations and providing clear diagnostics. We hope to introduce a new unit test for each bug encountered in BERI, and expand the test suite to provide detailed coverage of new ISA features.

# Chapter 5

# **BERI on Altera FPGAs**

This chapter describes how to build BERI for synthesis using Bluespec, configure the Altera build environment, and synthesize BERI for the Terasic DE4 FPGA development board described in later chapters. This information is relevant to researchers working with the BERI hardware design. Software consumers of BERI can find information on using specific Terasic boards in Chapter 6, and will not need to follow the directions in this chapter.

### **5.1 Building BERI for Synthesis**

BERI source code may be compiled to Verilog with the verilog target.

```

$ CAP=1 make verilog

$ ./sim

```

The BERI Verilog build is also sensitive to five make variables described in Section 2.5. The result of building BERI for synthesis is a set of Verilog files in the appropriate directory in ip/, with the file mkTopAvalonPhy.v containing the top-level module. These files may be copied into one of the directories in the boards/ directory to be synthesized for a particular board. As a note, when a supported FPGA board is connected to the computer by USB, it is possible to connect to the BERI UART using JTAG:

```

$ nios2-terminal --instance 0

```

## **5.2** The Altera Development Environment

Terasic's FPGA evaluation boards include Altera FPGAs; the following sections depend on the correct installation of Altera's FPGA development toolchain in order to synthesize and program the on-board FPGAs. Some of Altera's tools – especially the GUIs, but also some command-line tools – require X11; in these cases, if using a central build server, ensure that the -X argument is passed to the ssh command:

```

$ ssh -X user@zenith.cl.cam.ac.uk

```

You can also install Xvfb if you need to run without an X connection:

```

Xvfb :99

export DISPLAY=localhost:99

```

For some Altera tools to function under Ubuntu, /bin/sh must point to bash, and not dash, which is the default in Ubuntu. This should not be necessary for Quartus version 13.0 onwards.

There are two solutions:

1. Patch the Quartus 12.1 distribution so that scripts starting:

```

#!/bin/sh

now start

#!/bin/bash

(The Computer Lab uses this approach, and recommends it.)

```

2. Modify the symbolic link so that /bin/sh links to /bin/bash. Although we've never found a problem with this solutions, it seems inelegant and runs the risk of breaking some aspect of your Linux setup.

To configure your shell to use Bluespec, Altera, and other development toolchain elements for BERI (such as compilers and linkers), use the following script from the BERI distribution or CTSRD Subversion repository (described in previous chapters):

```

$ cd cheri/trunk

$ source setup.sh

```

In order to successfully build the BERI hardware project, ensure that you have added the Bluespec Verilog library to the Quartus global library path. This library is typically located at:

```

<BluespecDirectory>/lib/Verilog

```

Also ensure that you have added any relevant license files needed to build the project. For example, if you are using an Terasic touchscreen, you may need to add the license file for the i2c\_touch Verilog module to the license file string for Quartus.

Finally, if you are using Ubuntu, you may need to insert a new rules file into /etc/udev/rules.d/ to allow otherwise unprivileged users to access the USB-Blaster JTAG interface. You might add a new file named 51-usbblaster.rules with the following contents:

```

# Set permissions for Altera USB Blaster

SUBSYSTEM=="usb", ATTR{idVendor}=="09fb", ATTR{idProduct}=="6001", \

MODE="0666", OWNER="root", GROUP="dialout"

# Set permissions for Fast Altera USB2 Blaster

SUBSYSTEM=="usb", ATTR{idVendor}=="09fb", ATTR{idProduct}=="6810", \

MODE="0666", OWNER="root", GROUP="dialout"

```

| Directory                      | Board       |

|--------------------------------|-------------|

| cheri/trunk/boards/terasic_de4 | Terasic DE4 |

Table 5.1: Terasic per-board directories

| Target            | Description                                           |

|-------------------|-------------------------------------------------------|

| all               | builds everything using the following steps (except   |

|                   | download)                                             |

| build_cheri       | builds the BERI processor                             |

| build_peripherals | builds the peripherals                                |

| build_miniboot    | builds miniboot ROM and copy initial.hex here         |

| build_qsys        | builds Qsys project containing BERI, etc.             |

| build_fpga        | synthesize, map, fit, analyze timing, and generate    |

|                   | FPGA image                                            |

| report_critical   | scans build_fpga reports for critical warnings        |

| report_error      | scans build_fpga reports for errors                   |

| download          | attempts to download the FPGA (.sof) image to the     |

|                   | FPGA but the chain file (.cdf) may need to be updated |

|                   | for your configuration (e.g. USB port number)         |

| clean             | removes Quartus and Qsys build files                  |

| cleanall          | clean + clean peripherals, BERI and miniboot          |

Table 5.2: Make targets for per-board directories

## **5.3** Synthesizing BERI

The CTSRD project provides reference configurations for BERI on the Terasic DE4 board; per-board directories are listed in Table 5.1. Each board directory contains its own Quartus project, Makefile, etc. Table 5.2 shows the available make targets.

Targets build\_cheri and build\_peripherals cause other Makefiles to be used to build various Verilog components that are found by Quartus via the paths in peripherals.ipx and processors.ipx. build\_miniboot compiles the miniboot loader C code and produces a ROM image initial.hex. which is copied into the board directory.

A make cleanall; make all will take around 40 minutes to an hour to complete on a fast PC. The generated .sof file can be downloaded to an FPGA using the Quartus GUI or berictl – see the *BERI Software Reference* for more details.

# Chapter 6

# **BERI on Terasic Boards**

This chapter describes how to use the BERI processor prototype on the Terasic DE4 development board; there is also reference information on the Terasic tPad teaching board, but this is not well-supported with current versions of BERI. The chapter includes tutorial material on programming the board and on how board peripherals are exposed to BERI in the reference designs provided by the CTSRD project. This chapter is intended to support software development on BERI. See Chapter 5 for documentation pertinent to hardware development.

# 6.1 BERI Configuration on Terasic FPGA Boards

Communication with external I/O devices, such as NICs, is accomplished via a blend of memory-mapped I/O, interrupts, and (eventually) DMA. The BERI processor and operating system stack supports a variety of peripherals ranging from Altera "soft" cores, such as the JTAG UART and SD Card IP cores, to "hard" peripherals provided by Terasic on its tPad and DE4 development boards. The following sections document available peripherals and their configuration on the Avalon system-on-chip bus as configured in the BERI reference designs.

## 6.1.1 Physical Address Space on the DE4

Table 6.1 shows the physical addresses reserved for I/O devices in the BERI reference DE4 configuration.

## 6.1.2 Physical Address Space on the tPad

Table 6.2 shows the physical addresses reserved for I/O devices in the BERI reference tPad configuration.

#### 6.2 Altera IP Cores

BERI and FreeBSD support a number of Altera "soft" IP cores on the Terasic tPad and DE4 platforms. Many of these IP cores are documented in the *Embedded Peripherals IP User Guide*<sup>1</sup> provided by Altera, including the JTAG UART core and Avalon-MM and Avalon-ST bus attachments.

http://www.altera.com/literature/ug/ug\_embedded\_ip.pdf

| Base address | Length | IRQ | Description                                           |  |

|--------------|--------|-----|-------------------------------------------------------|--|

| 0x7000000    | 128 MB | -   | Cambridge Multitouch LCD + 256 Mb Intel StrataFlash   |  |

| 0x7f000000   | 64     | 0   | Altera JTAG UART                                      |  |

| 0x7f001000   | 64     | 7   | Altera JTAG UART for debugging output                 |  |

| 0x7f002000   | 64     | 8   | Altera JTAG UART for data                             |  |

| 0x7f004000   | 4      | -   | Old location of count register until 2013-03-01       |  |

| 0x7f005000   | 1024   | -   | Altera Triple-Speed Ethernet MegaCore MAC control     |  |

|              |        |     | Port 1                                                |  |

| 0x7f005400   | 8      | -   | MAC transmit FIFO                                     |  |

| 0x7f005420   | 32     | 11  | MAC transmit FIFO control <sup>1</sup>                |  |

| 0x7f005500   | 8      | -   | MAC receive FIFO                                      |  |

| 0x7f005520   | 32     | 12  | MAC receive FIFO control <sup>2</sup>                 |  |

| 0x7f006000   | 1      | -   | DE4 LEDs, one bit per LED                             |  |

| 0x7f007000   | 1024   | -   | Altera Triple-Speed Ethernet MegaCore MAC control     |  |